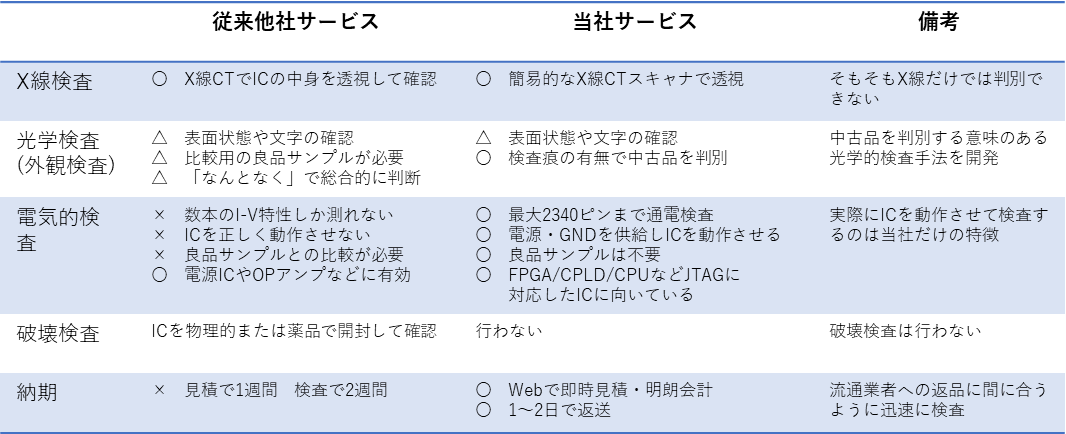

他社サービスとの違い

シン・ICと従来の真贋判定の違い

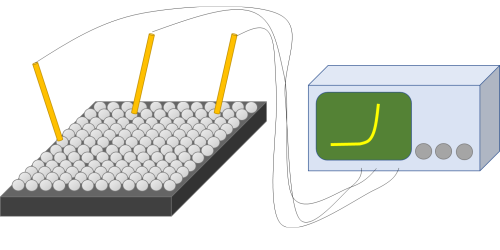

従来の電気的検査

従来の電気的検査は、マニュアルプローバやカーブトレーサという測定器を使ってI-V特性を測ります。具体的にはICの任意の何個かのピンに電圧を加えていって電圧と電流の関係を見るのですが、この方法には3つの大きな問題があります。

① ディジタルICにI-V検査は意味をなさない

ICの端子に電圧を加えていって流れる電流を測るという検査は、ICの本来の使い方とは大きく異なる使い方になります。一般的にディジタルICは端子に保護用のダイオードが入っていて、I-V検査はこの保護ダイオードの特性を見ているにすぎません。しかし、ダイオードがONする電圧を加えてしまうと破壊してしまう可能性があります。

ディジタルICに対するI-V検査は、保護ダイオードの特定を見るという程度のことしかできません。

② すべてのピンを検査することはできない

I-V検査はマニュアルプローバを用いて端子に接触しますが、FPGAなどでは数十から2000個ほどのピンがあるので、すべての端子を測ることは現実的ではありません。一般的には、どの端子を測定するかを顧客が指定することになります。

③ 比較用の正規品サンプルが必要

I-V検査では比較用の正規品さサンプルが必要になります。もともとI-V検査はトランジスタやFETでは意味がある検査ですが、大規模なディジタルICにとっては意味がないばかりか、壊してしまう可能性があります。このような危険性があるのにディジタルICの機能を見るものとしては全く意味がありません。

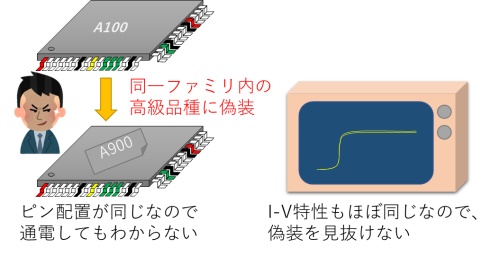

I-V検査では同一ファミリでの偽装を発見しにくい

もし、カーブトレーサを使って電源投入時の電圧-電流特性や、ピン間のI-V特性が得られたとしても、中古品や同一ファミリのマーキング書き換え品はピン配置が同じであったり、I-V特性もほぼ同じであったりするため、電圧と電流を見ていても本物か偽物かを断定できないでしょう。

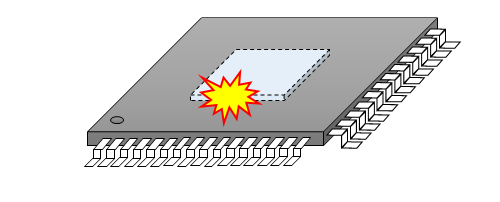

異常のあるピンに偶然当たる確率は低い

中古品のICで一部の端子が壊れているような場合、I-V特性を測らなかった端子が壊れていたら見過ごしてしまうことになります。

I-V特性はマニュアルプローバという機械を使って1つ1つのピンに針を刺して行うので、全ピンを検査することは現実的ではありません。たくさんのピンがあるICで、異常がある1つのピンに偶然針を刺すという確率は高くはないでしょう。

従来のやり方でI/Oの電気的検査を行うには、FPGAやCPUを動作させるプログラムを作成して書き込み、オシロスコープなどで波形を観察するという非常に工数のかかる方法でしかできませんでした。こういった検査は特定のICに対しては行えるかもしれませんが、汎用的にできるものではありません。

当社の電気的検査

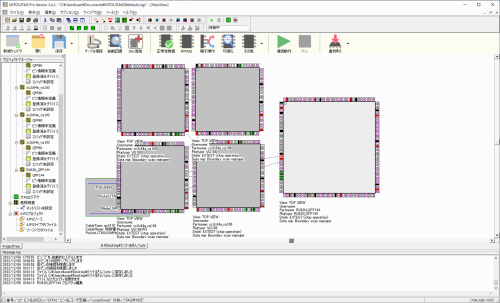

ソケットを使ってVCC,GND,JTAGを供給

当社の検査ではQFP64からBGA1754まで約20種類の標準的なICソケットを用意し、全ての電源とGNDを正しく供給した上で実際に動作させます。

JTAGを通じてIDCODEを読み取ったり、バウンダリスキャンによって端子を操作して信号を出すという機能検査を行います。IDCODEが異なる偽物や読み取れない故障品は100%排除できます。

JTAGバウンダリスキャンで全ピン検査

JTAGバウンダリスキャンによって全I/Oピンの入出力検査を行います。これによって静電気で破壊されているピンがないかどうかや、ボンディングワイヤが切れているようなピンがないかといったことがわかります。

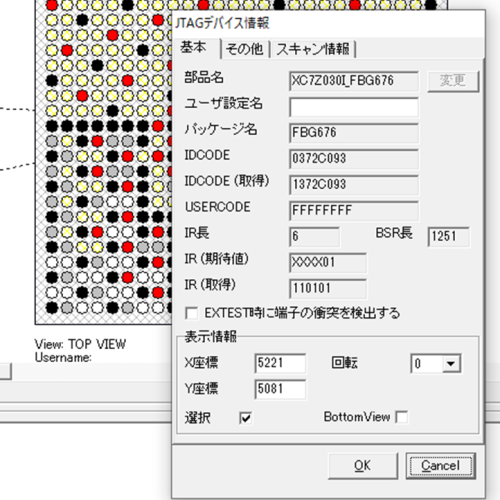

JTAG IDCODEでデバイスの種類を判別

FPGAやCPU、CPLDといった大規模ディジタルICはJTAGという検査機能をもともと持っていて、JTAGに対応したICには種類ごとに固有のIDCODEがあります。このIDCODEを確認することで本物のICかどうかを判断することができます。

もし、ピン配置が同じである同一ファミリ内の偽装※があった場合でも、JTAG IDCODEの照合によって偽装を見抜くことができます。

当社の検査は多ピンのディジタルIC、特にFPGAに特化されています。OPアンプや電源IC、小規模ロジックICの検査には不向きです。

※XC7A100をXC7A200と偽る、RX62NをRX63Nと偽るなど

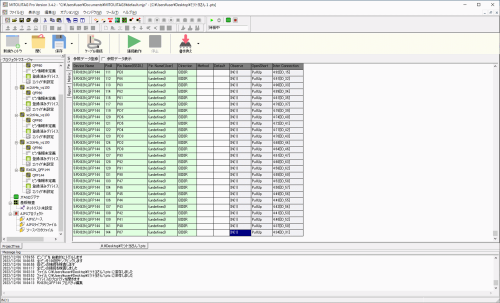

従来の手法と、当社の手法のまとめ

従来のX線・外観・電気的検査による真贋判定と、当社が提供する真贋判定方法の比較を以下の表に示します。